Hmm, trying to measure the frequency content of a IC's power current strikes me as the wrong way to go about fixing a RFI problem. Assume the worst about the IC's current frequency and design to that. Even if you measure something, you won't have any guarantee it's the worst case for all operations, over all production lots, over all temperatures, etc.

So pretend you did the measurements and found crap everywhere. Now go fix that.

It's all about visualizing the high frequency current loops and minimizing their areas. The first line of defense is good bypass caps with the shortest possible leads between the power and ground pins. Realize that at high frequencies, the IC is a current generator. The bypass caps shunt this current to short loops close to the IC.

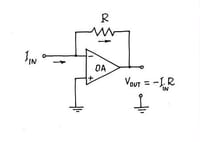

The next thing is to keep the high frequency current off your ground plane. The only difference between a ground plane and a center fed patch antenna is what you're driving it with. Your attached picture is a good diagram of now NOT to do it. If this is a large IC with several power and ground pins, make separate power and ground nets just local to the IC. The bypass caps are connected between these nets, which are carefully layed out under and nearby the IC. Other components that handle high frequencies directly related to that IC run off the same power and ground nets. A crystal and its two caps is a good example. The crystal caps go back to the local IC ground, not the ground plane.

Eventually the local power and ground nets connect to the board's wider power and ground nets, but they do this at single points, preferably with a little larger cap right accross the IC side of those single point connections. For example, you might use 1uF bypass caps, so use a 10uF second tier bypass cap between the two nets right where they connect to the rest of the board. The whole strategy is to contain the inevitable high freuqency loop currents. The current that flows thru the two connection points to the rest of the board then will contain substantially lower high frequency content, which in turn will feed less RF into the patch antenna you call a ground plane. And the little it does feed will have very little differential mode signal because the two connection points are physically close together.

I've done this sort of thing a bunch of times. Sometimes if it's more than a two layer board, you can afford a small sub-ground plane just under the IC and its immediate surrounds on a different layer than the main ground plane. This is the local ground net I described above. This sub-ground plane punches thru to the main ground plane in exactly one spot, which is right next to where the local power net connects to the main power net, with a second tier bypass cap right accross the two points.