I

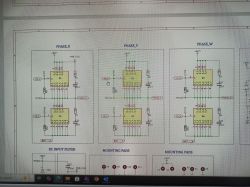

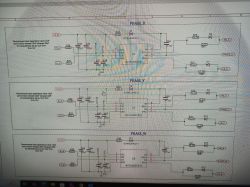

I am facing an unintended turn-on issue in a three-phase inverter (half-bridge leg).

When the high-side MOSFET turns on, the switching node experiences a dv/dt as Vds of the high-side device falls rapidly. This dv/dt couples through the Miller capacitance (Cgd) of the low-side MOSFET. As a result, a positive voltage spike appears at the low-side gate, even though the gate driver is commanding it off.

This induced gate voltage rise causes momentary low-side turn-on, leading to shoot-through in the inverter leg.

Observations:

Under light-load conditions, the induced Vgs spike was initially around 2 V.

After tuning, I reduced the spike to approximately 0.8 V, which is below the threshold voltage and seems safe at low load.

However, when the load current increases, the gate voltage hump increases again and approaches the MOSFET threshold voltage. The issue becomes more severe at higher load current, likely due to increased di/dt and dv/dt.

Mitigation Steps Already Tried:

Increased gate turn-on resistance from 2.2 Ω to 33 Ω

Decreased gate turn-off resistance from 5.1 Ω to 2.2 Ω. Added external gate-to-source capacitor up to 15 nF

Tuned RC snubber across the switch.

Implemented an external Miller-clamp circuit using a PNP transistor MOSFET, part number (FDBL86062_F085-ONSEMI).

These methods reduced the spike under light load but did not fully eliminate the issue under higher load conditions.

What would be a robust and permanent solution to prevent Miller-induced turn-on of the low-side MOSFET at higher load currents?

AI: Could you provide details about the gate driver IC you are using (part number, source/sink current capability, and whether it has a built-in Miller clamp or other relevant features)?

Yes

AI: Can you share information about your PCB layout, specifically regarding gate drive trace lengths, gate loop inductance, and how the low-side source is referenced to the driver and power ground?

Yes