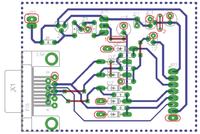

It is a Si Prog programmer. I know that the paths would be able to lead better, more minimalist. I will make the plate using the thermal transfer method

Czy wolisz polską wersję strony elektroda?

Nie, dziękuję Przekieruj mnie tam

maciek114411 wrote:place here - in a packed form, eg ZIP or RAR, attach the whole project.

maciek114411 wrote:it lasted a bit, because I had more urgent matters, and besides, the need was to devote a lot of time to the analysis of this, something here posted.I'm in a hurry

milosek wrote:Only that on - see above - PCB drawing does not show this and no switching on / off layers does not change this.As for these hanging pads I do not have any objections, because after using the tool Ratsnest the mass field is poured nicely by combining the previously hanging points.

milosek wrote:You can not see anything here, that's why I changed the background from black to white - see above - and then you do not see those connections.

maciek114411 wrote:Look there: post # 10 , is there something visible there?I do not understand too much what's going on and what to improve. For me, how do I download this file that I previously put in and I click ratsnest GND is properly spilled and all connections are made. Even the first picture is with properly poured GND. These grommets are not unnecessary, they combine the field of mass. And as for the white background, I changed it and GND is still properly spilled, you had to remove it by mistake. Unfortunately, there is no possibility (or at least I can not) save the file so that after opening the mass field was visible was visible, it is always marked with an interrupted line and only after clicking ratsnest reveals itself

I wanted to check the PCB in terms of functioning or how it will build it will work? Does it have any errors?

maciek114411 wrote:Unfortunately, but it does not work for me.If you want to see all connections, download this PCB file again and after downloading click ratsnest in [e] E agl e'u

maciek114411 wrote:Thank you ...

maciek114411 wrote:

Quarz wrote:The PCB design presented above seems to be correct and in accordance with the schematic diagram.maciek114411 wrote:I will reply at the earliest tomorrow ...So I'm waiting for opinions about PCBs?

All good?

maciek114411 wrote:You can do it - put a virtual pad on it and then a thinner path on one side and a thicker one on the other.I led one whole path differently (I released it under RS232). And in the second I can not do much better with tin than with the pickle.

maciek114411 wrote:Please ...Thanks for your help

maciek114411 wrote:View TU - this is the accepted standard - but it does not suit me with the standard adopted there and on the site of the original design SI-Prog is different - see description -> AVR microcontroller adapterAnd yet someone could write which goldpiny is [mosi miso sck and reset] MOSI MISO SCK and RESET .

maciek114411 wrote:For this answer question, look in DataSheet for a specific ?CPU.There is a 4 MHz quartz resonator drawn on that schematic. Is it superfluous to be able to program the microcontroller on the internal oscillator?

TL;DR: 77 % of first-time Eagle users miss a GND tie [PCBWay, 2022]. “The PCB design … is correct” [Elektroda, Quarz, post #12410650] Use Ratsnest or Eagle 6.4+ to show the poured ground, then widen the two thinnest tracks.

Why it matters: A single missed ground or thin trace can turn an otherwise functional Si Prog into an unresponsive board.

• Recommended DIY trace width (toner transfer): 0.25 mm / 10 mil [FabAcademy, 2021] • Si Prog supports AVR ISP at 5 V, up to 12 MHz target clock [Lancos, 2019] • Eagle 6.4.0 added live polygon preview; older versions hide pours until Ratsnest [Autodesk, 2013] • Typical single-sided PCB home-etched cost ≈ €2 for 5 × 5 cm [HomePCB, 2020] • 0.25 mm copper track carries ≈ 1 A with 10 °C rise on 35 µm copper [Saturn PCB Toolkit, 2022]