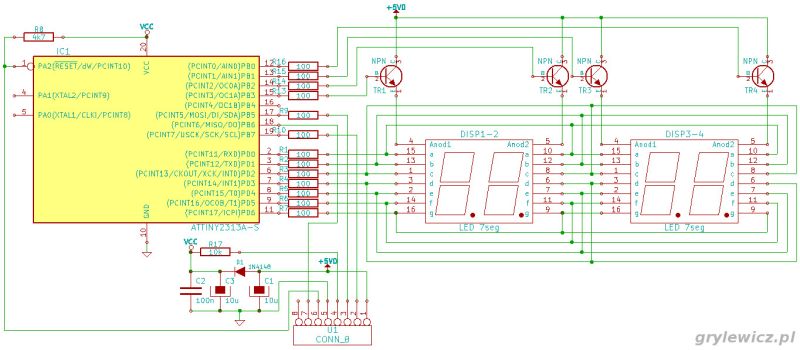

;*************************************************************

; Echostar_dsb-717 *

; avr-objdump -D -m avr:4 flash_tiny.hex >flash_tiny.txt *

;*************************************************************

.include "tn2313.inc"

.def acc = r16

.equ sda = 5

.equ scl = 7

.org 0x0000

;-------------------------------------------------------------

rjmp Reset ; 0x1f6 0: c0fa

reti ; 2: 9518

reti ; 4: 9518

reti ; 6: 9518

reti ; 8: 9185

reti ; a: 9518

reti ; c: 9518

reti ; e: 9518

reti ; 10: 9518

reti ; 12: 9518

reti ; 14: 9518

reti ; 16: 9518

reti ; 18: 9518

rjmp OC0A ; 0x1c0 1a: c0d2

reti ; 1c: 9518

rjmp USI_START ; 0x40 1e: c010

reti ; 20: 9518

reti ; 22: 9518

reti ; 24: 9518

;-------------------------------------------------------------

Data_Data:

.db 0x08, 0x65 ; 26: 6508

.db 0x00, 0x00 ; 28: 0000

.db 0x05, 0x60 ; 2a: 6005

.db 0x54, 0x02 ; 2c: 0254

;-------------------------------------------------------------

Init_I2C:

cbi PORTB, scl ; 24 2e: 98c7

cbi PORTB, sda ; 24 30: 98c5

cbi DDRB, scl ; 23 32: 98bf

cbi DDRB, sda ; 23 34: 98bd

ldi acc, 0b1010_1000 ; 168 36: ea08

out USICR, acc ; 13 38: b90d

ldi acc, 0b1111_0000 ; 240 3a: ef00

out USISR, acc ; 14 3c: b90e

ret ; 3e: 9508

;-------------------------------------------------------------

;*************************************************************

;* Read I2c *

;*************************************************************

USI_START:

st -Y, XL ; 40: 93aa

st -Y, r25 ; 42: 939a

st -Y, r24 ; 44: 938a

st -Y, ZL ; 46: 93ea

st -Y, r18 ; 48: 932a

st -Y, r17 ; 4a: 931a

st -Y, acc ; 4c: 930a

in r18, SREG ; 63 4e: b72f

ldi acc, 0b1110_0000 ; 224 50: ee00

out USISR, acc ; 14 52: b90e

sei ; 54: 9478

Wait_00:

in acc, USISR ; 14 56: b10e

andi acc, 0b0000_1111 ; 15 58: 700f

cpi acc, 0b0000_1101 ; 13 5a: 300d

brcs Wait_00 ; 0x56 5c: f3e0

cli ; 5e: 94f8

Wait_01:

sbis USISR, USIOIF ; 14 60: 9b76

rjmp Wait_01 ; 0x60 62: cffe

in acc, USIDR ; 15 64: b10f

cpi acc, 0b0111_0000 ; 112 66: 3700

brne Set_USISR ; 0xc6 68: f571

ldi acc, 0x00 ; 0 6a: e000

out USIDR, acc ; 15 6c: b90f

sbi DDRB, sda ; 23 6e: 9abd

ldi acc, 0b0100_1101 ; 77 70: e40d

out USISR, acc ; 14 72: b90e

Wait_02:

sbis USISR, USIOIF ; 14 74: 9b76

rjmp Wait_02 ; 0x74 76: cffe

cbi DDRB, sda ; 23 78: 98bd

ldi acc, 0b1110_0000 ; 224 7a: ee00

out USISR, acc ; 14 7c: b90e

ldi r24, 0x00 ; 0 7e: e080

ldi r25, 0x00 ; 0 80: e090

Read_Loop:

sei ; 82: 9478

Wait_03:

in acc, USISR ; 14 84: b10e

andi acc, 0x0F ; 15 86: 700f

cpi acc, 0x0D ; 13 88: 300d

brcs Wait_03 ; 0x84 8a: f3e0

cli ; 8c: 94f8

Wait_04:

sbis USISR, USIOIF ; 14 8e: 9b76

rjmp Wait_04 ; 0x8e 90: cffe

ldi ZL, 0x65 ; 101 92: e6e5

in acc, USIDR ; 15 94: b10f

std Z+7, acc ; 0x07 96: 8307

ldi acc, 0x00 ; 0 98: e000

out USIDR, acc ; 15 9a: b90f

sbi DDRB, sda ; 23 9c: 9abd

ldi acc, 0x4E ; 78 9e: e40e

out USISR, acc ; 14 a0: b90e

Wait_05:

sbis USISR, USIOIF ; 14 a2: 9b76

rjmp Wait_05 ; 0xa2 a4: cffe

cbi DDRB, sda ; 23 a6: 98bd

ldd r17, Z+7 ; 0x07 a8: 8117

ldi r26, 0x65 ; 101 aa: e6a5

inc r26 ; ac: 95a3

add XL, r24 ; ae: 0fa8

st X, r17 ; b0: 931c

ldi acc, 0b1110_0000 ; 224 b2: ee00

out USISR, acc ; 14 b4: b90e

ldi acc, 0x01 ; 1 b6: e001

st Z, acc ; b8: 8300

adiw r24, 0x01 ; 1 ba: 9601

cpi r24, 0x06 ; 6 bc: 3086

ldi acc, 0x00 ; 0 be: e000

cpc r25, acc ; c0: 0790

brge Skip_Set_USISR ; 0xca c2: f41c

rjmp Read_Loop ; 0x82 c4: cfde

Set_USISR:

ldi acc, 0b1111_0000 ; 240 c6: ef00

out USISR, acc ; 14 c8: b90e

Skip_Set_USISR:

out SREG, r18 ; 63 ca: bf2f

ld acc, Y+ ; cc: 9109

ld r17, Y+ ; ce: 9119

ld r18, Y+ ; d0: 9129

ld ZL, Y+ ; d2: 91e9

ld r24, Y+ ; d4: 9189

ld r25, Y+ ; d6: 9199

ld XL, Y+ ; d8: 91a9

reti ; da: 9518

;*************************************************************

WATCHDOG:

cli ; dc: 94f8

wdr ; de: 95a8

in acc, WDTCR ; 33 e0: b501

ori acc, 0b0001_1000 ; 24 e2: 6108

out WDTCR, acc ; 33 e4: bd01

ldi acc, 0b0010_1001 ; 41 e6: e209

out WDTCR, acc ; 33 e8: bd01

sei ; ea: 9478

Return_from_Convertor:

ret ; ec: 9508

;-------------------------------------------------------------

Convertor:

mov r17, acc ; ee: 2f10

bst r17, 0 ; f0: fb10

ldi r17, 0x00 ; 0 f2: e010

bld r17, 2 ; f4: f912

mov r18, acc ; f6: 2f20

add r18, r18 ; f8: 0f22

add r18, r18 ; fa: 0f22

add r18, r18 ; fc: 0f22

or r18, r17 ; fe: 2b21

andi r18, 0b0001_0111 ; 23 100: 7127

mov r17, acc ; 102: 2f10

add r17, r17 ; 104: 0f11

andi r17, 0b0000_1000 ; 8 106: 7018

or r17, r18 ; 108: 2b12

mov r18, acc ; 10a: 2f20

lsr r18 ; 10c: 9526

lsr r18 ; 10e: 9526

andi r18, 0b0000_0010 ; 2 110: 7022

or r18, r17 ; 112: 2b21

mov r17, acc ; 114: 2f10

add r17, r17 ; 116: 0f11

andi r17, 0b0010_0000 ; 32 118: 7210

or r17, r18 ; 11a: 2b12

mov r18, acc ; 11c: 2f20

bst r18, 5 ; 11e: fb25

ldi r18, 0x00 ; 0 120: e020

bld r18, 0 ; 122: f920

or r18, r17 ; 124: 2b21

andi acc, 0b0100_0000 ; 64 126: 7400

or acc, r18 ; 128: 2b02

com acc ; 12a: 9500

rjmp Return_from_Convertor ; 0xec 12c: cfdf

;-------------------------------------------------------------

Set_Hardware:

in acc, DDRB ; 23 12e: b307

ori acc, 0b0000_1111 ; 15 130: 600f

out DDRB, acc ; 23 132: bb07

in acc, PORTB ; 24 134: b308

andi acc, 0b1111_0000 ; 240 136: 7f00

out PORTB, acc ; 24 138: bb08

in acc, DDRD ; 17 13a: b301

ori acc, 0b0111_1111 ; 127 13c: 670f

out DDRD, acc ; 17 13e: bb01

in acc, PORTD ; 18 140: b302

andi acc, 0b1000_0000 ; 128 142: 7800

out PORTD, acc ; 18 144: bb02

ldi acc, 0x03 ; 3 146: e003

ldi ZL, 0x60 ; 96 148: e6e0

st Z, acc ; 14a: 8300

in acc, TIMSK ; 57 14c: b709

andi acc, 0b1111_1100 ; 252 14e: 7f0c

out TIMSK, acc ; 57 150: bf09

ldi acc, 0x00 ; 0 152: e000

out TCNT0, acc ; 50 154: bf02

ldi acc, 0x20 ; 32 156: e200

out OCR0A, acc ; 54 158: bf06

in acc, TCCR0B ; 51 15a: b703

ori acc, 0b0000_0100 ; 4 15c: 6004

out TCCR0B, acc ; 51 15e: bf03

in acc, TIMSK ; 57 160: b709

ori acc, 0b0000_0001 ; 1 162: 6001

out TIMSK, acc ; 57 164: bf09

ldi acc, 0x38 ; 56 166: e308

rcall Init_I2C ; 0x2e 168: df62

ldi acc, 0xF0 ; 240 16a: ef00

rcall Convertor ; 0xee 16c: dfc0

ldi acc, 0x00 ; 0 16e: e000

ldi ZL, 0x65 ; 101 170: e6e5

st Z, acc ; 172: 8300

in r17, MCUSR ; 52 174: b714

sbrc r17, 3 ; 176: fd13

rjmp Skip_Set ; 0x186 178: c006

ldi acc, 0xFF ; 255 17a: ef0f

ldi ZL, 0x6D ; 109 17c: e6ed

std Z+3, acc ; 0x03 17e: 8303

std Z+2, acc ; 0x02 180: 8302

std Z+1, acc ; 0x01 182: 8301

st Z, acc ; 184: 8300

Skip_Set:

ldi acc, 0x00 ; 0 186: e000

out MCUSR, acc ; 52 188: bf04

rcall WATCHDOG ; 0xdc 18a: dfa8

;-------------------------------------------------------------

Main:

Wait_Hear:

wdr ; 18c: 95a8

ldi ZL, 0x65 ; 101 18e: e6e5

ld acc, Z ; 190: 8100

and acc, acc ; 192: 2300

breq Wait_Hear ; 0x18c 194: f3d9

ldi acc, 0x00 ; 0 196: e000

st Z, acc ; 198: 8300

cli ; 19a: 94f8

ldi r24, 0x00 ; 0 19c: e080

ldi r25, 0x00 ; 0 19e: e090

Loop:

mov acc, r24 ; 1a0: 2f08

subi acc, 0xFE ; 254 1a2: 5f0e

mov ZL, acc ; 1a4: 2fe0

subi ZL, 0x9A ; 154 1a6: 59ea

ld acc, Z ; 1a8: 8100

rcall Convertor ; 0xee 1aa: dfa1

ldi ZL, 0x6D ; 109 1ac: e6ed

add ZL, r24 ; 1ae: 0fe8

st Z, acc ; 1b0: 8300

adiw r24, 0x01 ; 1 1b2: 9601

cpi r24, 0x04 ; 4 1b4: 3084

ldi acc, 0x00 ; 0 1b6: e000

cpc r25, acc ; 1b8: 0790

brlt Loop ; 0x1a0 1ba: f394

sei ; 1bc: 9478

rjmp Main ; 0x18c 1be: cfe6

;*************************************************************

;* 7 Seg Led Diplay Interrupt *

;*************************************************************

OC0A:

st -Y, ZL ; 1c0: 93ea

st -Y, r17 ; 1c2: 931a

st -Y, acc ; 1c4: 930a

in r17, SREG ; 63 1c6: b71f

ldi acc, 0x00 ; 0 1c8: e000

out TCNT0, acc ; 50 1ca: bf02

out PORTB, acc ; 24 1cc: bb08

ldi ZL, 0x60 ; 96 1ce: e6e0

ld ZL, Z ; 1d0: 81e0

subi ZL, 0x93 ; 147 1d2: 59e3

ld acc, Z ; 1d4: 8100

out PORTD, acc ; 18 1d6: bb02

ldi ZL, 0x60 ; 96 1d8: e6e0

ld ZL, Z ; 1da: 81e0

subi ZL, 0xA0 ; 160 1dc: 5ae0

ldd acc, Z+1 ; 0x01 1de: 8101

out PORTB, acc ; 24 1e0: bb08

ldi ZL, 0x60 ; 96 1e2: e6e0

ld acc, Z ; 1e4: 8100

inc acc ; 1e6: 9503

andi acc, 0b0000_0011 ; 3 1e8: 7003

st Z, acc ; 1ea: 8300

out SREG, r17 ; 63 1ec: bf1f

ld acc, Y+ ; 1ee: 9109

ld r17, Y+ ; 1f0: 9119

ld ZL, Y+ ; 1f2: 91e9

reti ; 1f4: 9518

;*************************************************************

;-------------------------------------------------------------

Reset:

ldi acc, 0xB0 ; 176 1f6: eb00

out SPL, acc ; 61 1f8: bf0d

ldi YL, 0x91 ; 145 1fa: e9c1

rcall Down_020a ; 0x20a 1fc: d006

and acc, acc ; 1fe: 2300

breq Skip_Read_Data ; 0x204 200: f009

rcall Read_Data ; 0x222 202: d00f

Skip_Read_Data:

rcall Set_Hardware ; 0x12e 204: df94

rcall Go_to_Sleep ; 0x24e 206: d023

rjmp Go_to_Sleep ; 0x24e 208: c022

Down_020a:

ldi acc, 0x01 ; 1 20a: e001

ret ; 20c: 9508

Clear_Ram:

ldi r17, 0x00 ; 0 20e: e010

st X+, r17 ; 210: 931d

dec acc ; 212: 950a

brne Clear_Ram ; 0x20e 214: f7e1

Return_Set_Ram_Data:

ret ; 216: 9508

Set_Ram_Data:

lpm r17, Z+ ; 218: 9115

st X+, r17 ; 21a: 931d

dec acc ; 21c: 950a

brne Set_Ram_Data ; 0x218 21e: f7e1

rjmp Return_Set_Ram_Data ; 0x216 220: cffa

Read_Data:

ldi r24, low (Data_Data << 1) ; 38 222: e286

ldi r25, high(Data_Data << 1) ; 0 224: e090

Loop1:

movw ZL, r24 ; 226: 01fc

lpm acc, Z+ ; 228: 9105

lpm XL, Z ; 22a: 91a4

movw ZL, r24 ; 22c: 01fc

adiw ZL, 0x02 ; 2 22e: 9632

lpm r18, Z+ ; 230: 9125

lpm r19, Z ; 232: 9134

mov r17, r18 ; 234: 2f12

or r17, r19 ; 236: 2b13

breq Go_Clear_Ram ; 0x240 238: f019

movw ZL, r18 ; 23a: 01f9

rcall Set_Ram_Data ; 0x218 23c: dfed

rjmp Skip_Clear_Ram ; 0x242 23e: c001

Go_Clear_Ram:

rcall Clear_Ram ; 0x20e 240: dfe6

Skip_Clear_Ram:

adiw r24, 0x04 ; 4 242: 9604

ldi r17, 0x00 ; 0 244: e010

cpi r24, 0x2E ; 46 246: 328e

cpc r25, r17 ; 248: 0791

brcs Loop1 ; 0x226 24a: f368

rjmp Return_Set_Ram_Data ; 0x216 24c: cfe4

Go_to_Sleep:

nop ; 24e: 0000

Go_Sleep:

sleep ; 250: 9588

rjmp Go_Sleep ; 0x250 252: cffe

Ram_Data:

.db 0x00, 0x08 ; 254: 0800

.db 0x04, 0x02 ; 256: 0204

.db 0x01, 0xff ; 258: ff01

;-------------------------------------------------------------

.exit

[img-1]

[img-1]