jarekgol wrote:piotr_go wrote:what does it mean?in LCSC they have C19

Flu v4.xx

Czy wolisz polską wersję strony elektroda?

Nie, dziękuję Przekieruj mnie tam

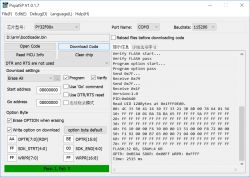

witawat57 wrote:How to download the program to mcu PY32F002A in Windows?

witawat57 wrote:Can st-link V2 be used?

source [find interface/cmsis-dap.cfg]

source [find target/swj-dp.tcl]

source [find mem_helper.tcl]

adapter speed 270

swd newdap puya cpu -enable

dap create puya.dap -chain-position puya.cpu

target create puya.cpu cortex_m -dap puya.dap

flash bank puya.flash puyaf0x 0x08000000 0x8000 0 0 puya.cpu

init

{

"version": "0.2.0",

"configurations": [

{

"name": "Cortex Debug",

"cwd": "${workspaceFolder}",

"executable": "${workspaceFolder}/build/puya_playground.out",

"request": "launch",

"type": "cortex-debug",

//"breakAfterReset": true,

"runToEntryPoint": "main",

"servertype": "openocd",

"configFiles": [

"openocd.cfg"

],

},

{

"name": "pyOCD",

"cwd": "${workspaceFolder}",

"type": "cortex-debug",

"request": "launch",

"executable": "${workspaceFolder}/build/puya_playground.out",

"servertype": "pyocd",

"targetId": "PY32F030x6",

"svdFile": "CMSIS/Device/PY32F0xx/py32f030xx.svd",

"svdPath": "CMSIS/Device/PY32F0xx/py32f030xx.svd",

"showDevDebugOutput":"none",

},

]

}

dabyd64 wrote:Do they have embedded bootloader?

What software to use?

Quote:

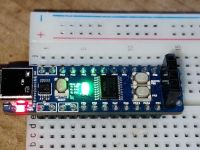

IMG_20230630_202656_1_1280x960.jpg

(322.81 KB)

You must be logged in to download this attachment.

IMG_20230630_202656_1_1280x960.jpg

(322.81 KB)

You must be logged in to download this attachment.

IMG_20230630_202624_1_1280x960.jpg

(219.1 KB)

You must be logged in to download this attachment.

IMG_20230630_202624_1_1280x960.jpg

(219.1 KB)

You must be logged in to download this attachment.

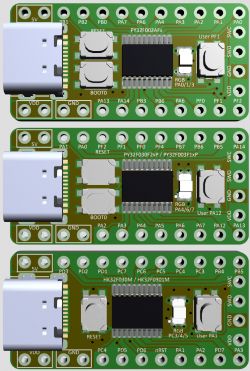

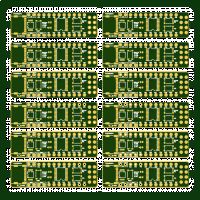

PY32F002_GERBER_6x2_PANEL_Top.png

(450.1 KB)

You must be logged in to download this attachment.

PY32F002_GERBER_6x2_PANEL_Top.png

(450.1 KB)

You must be logged in to download this attachment.

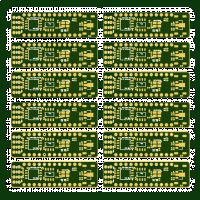

PY32F002_GERBER_6x2_PANEL_Bottom.png

(392.08 KB)

You must be logged in to download this attachment.

PY32F002_GERBER_6x2_PANEL_Bottom.png

(392.08 KB)

You must be logged in to download this attachment.

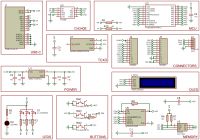

PY32F002_SCH.png

(114.98 KB)

You must be logged in to download this attachment.

PY32F002_SCH.png

(114.98 KB)

You must be logged in to download this attachment.

PY32F002_3D.png

(224.92 KB)

You must be logged in to download this attachment.

PY32F002_3D.png

(224.92 KB)

You must be logged in to download this attachment.

TL;DR: PUYA’s PY32F002 ARM-M0+ MCU costs just 0.08 USD, "surprisingly good for such a ridiculous price" [Elektroda, l0ud, post #20366259], and draws ~5 µA in sleep [Elektroda, piotr_go, post #20364764] Ideal for ultra-low-cost 32-bit projects.

Why it matters: You can replace 8-bit parts with a faster, pin-compatible ARM for pocket change.

• Core: Cortex-M0+ @ 24 / 32 MHz, up to 96 MHz overclocked [Elektroda, piotr_go, post #20380514] • Memory: 20 kB FLASH / 3 kB RAM (002) — hidden 32 kB FLASH / 4 kB RAM in some lots [Elektroda, piotr_go, post #20375532] • Peripherals: SPI, USART, I²C, ADC, timers; DMA on 003 & many 002 samples [Elektroda, l0ud, post #20366259] • Supply: 1.7 – 5.5 V, 5 µA sleep current [Elektroda, piotr_go, post #20364764] • Price: 0.08 USD each-1000, $0.20 retail at LCSC [Elektroda, piotr_go, #20364764; LCSC pricing]

JLinkExe, then loadfile firmware.hex.

Done in under a minute.reset halt; flash erase_sector 0 0 last over OpenOCD. Bootloader lock bits clear, proven on QFN20 parts [Elektroda, wichers, post #20525933]