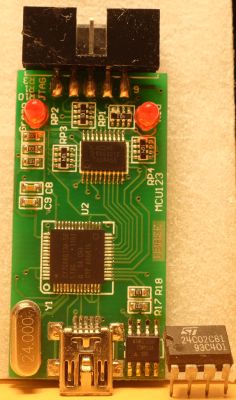

The presented microproject was created due to the damaged eeprom memory content in the logic analyzer clone on the CY7C68013A, commonly sold as saleae 8ch / 24MHz.

Once the analyzer refused to obey, I decided to get acquainted with the topic a bit. Replacing and programming the eeprom with the correct data would be too trivial as usual (I know that it can be done with the console from CY), so I decided to use the eeprom emulation library written there on tiny13 in order to switch the device ID to work with usbeeSX or saleae . The third mode with disconnected eeprom forces the default identification, which in the sigrok software starts 16 channels, but to use them you need to convert the analyzer, which I am going to do with the second device without a buffer.

The identifier is switched when the system is powered multiple times in less than 3 seconds. In normal connection and disconnection, vid / pid does not change. Installing tiny13 instead of eeprom only requires lifting the reset leg or disabling it while programming. In my case, I preferred to cut off the ground paths blocking the potential possibility of reprogramming the processor on the target pcb (with a clip).

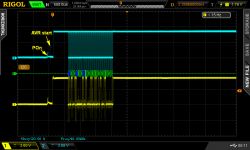

The program in the emulator pretends to be 16B eeprom memory, it is not writable, and it does not support the address pointer download command. The memory after these 16Bs is scrolled to the beginning. However, this does not prevent the software from working properly, as well as when booting the CY7C68013A. For me it was a surprise to include 'clock stretching'. When low level SCL is encountered, the eeprom reading is delayed.

Maybe someone will need such an emulator also for other applications.

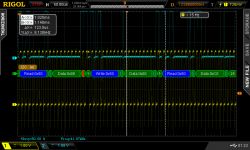

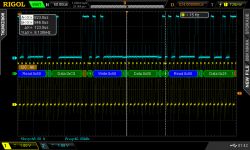

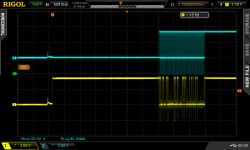

Below are a few oscillograms from the fun of writing pid changer. In the attachment hex with the source.

Cool? Ranking DIY