Congratulations on implementing an interesting project. Let me ask, have you carved your own BIOS for CP / M from scratch in Z80 assembly language? You made the so-called deblocking for SD card? Did you take any approach to CP / M 3.0?

I've been working on something like that for three years, too, but it's an 8080 project. It's also a much more retro layout. I even have FDD support and a completely self-written BIOS in 8080 assembly language. I also did deblocking for FDD. Other interesting facts include the LPT interface for the printer, the light pen and the RS232C mouse. The keyboard is also typical for a PC, but with a DIN connector. I also ran CP / M 2.2 and a whole bunch of period software. I am planning to add, among others stations 5.25 "in addition to the current 3.5".

As for the indicator devices, making the light pen is more difficult than it looks due to the jitter involved. This only works on the bright spots of the screen. However, even then, the effect is not always perfect. The mouse, on the other hand, works great. However, for this screen resolution, the transmitted shift must be divided by 2. I also wrote a simple "graphic" program in Pascal Mt +. I referenced additional BIOS functions that I did through assembly language snippets. The end result is quite good.

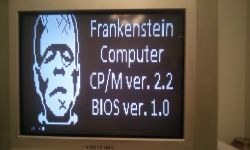

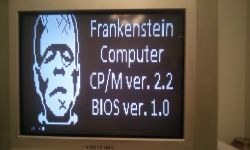

Start screen:

DIR command for USER 0:

Ladder platform game:

Microsoft BASIC and loading BUNNY.BAS (from the book "101 BASIC Computer Games"):

Code snippet (LIST command):

This program prints the Playboy bunny on a printer:

Effects of work in the MOUSE program that I wrote in Pascal MT +:

Terminal type change (one of the few extra commands I added to CP / M):

TINY BASIC for CP / M:

I also had fun with the muMATH program, which also appears as muSIMP:

It is something like a modern MATLAB / SCILAB / OCTAVE-style environment for CP / M. It has really big possibilities, e.g. differentiating formulas, integrating (indefinite integrals) etc.

Light pen:

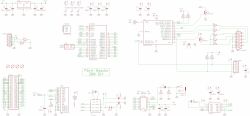

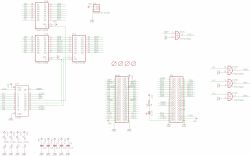

Motherboard:

General view of the whole:

Generally, as you can see, the image is quite good and legible. However, a lot depends on the TV (band of the vision amplifier, screen diagonal, overall tuning - convergence, sharpness, geometry, etc.).