Hello

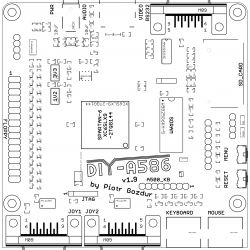

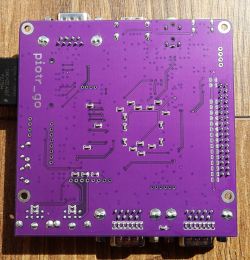

I would like to present the 1.9 DIY-A586 version, with the modifications that have come to my mind over the years. I skipped a few numbers so that I would not be tempted by another v1.x from XC6SLX9

Differences: 32MB RAM, JOY1 / 2 without multiplexing, 2 flopps without additional circuits, 18.432MHz generator, space for THT LEDs, 5k1 USB-C pull-downs, various minor fixes.

The board has:

- FPGA Spartan6 XC6SLX9

- 32MB 16bit SDRAM memory

- 16MB flash for core and ROMs

- HDMI output

- analog audio output + tape recorder input

- SD slot

- RS232

- 2 * joystick port

- 2 * PS / 2

- A500 keyboard connector

- floppy disk drive connectors

- 2 buttons (menu and reset)

- 2 LEDs

- 5V USB-C power socket

- dimensions 100x100mm

There are up to 30 configurations in flash that can be loaded into an FPGA.

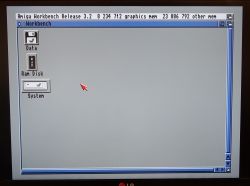

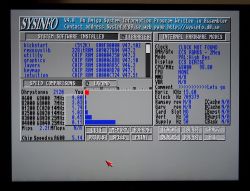

Mikan core (8MB CHIP, 23.5MB FAST) :

I thought it would fail, but somehow the 8MB DMA CHIP came in.

Diagram and gerberas in the appendix.

Commercial use prohibited.

Cool? Ranking DIY