Hi

@piotr_go congratulations on the next installment of the project ;)

As a total layman in FPGA systems, I have a few questions, and I am still before the stage of blinking the diode

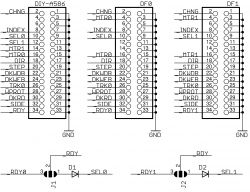

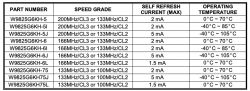

Let's assume that I would like to run DIY-a586 on e.g. tango nano 9k, how do I know that the FPGA data is sufficient to simulate the given peripherals?

Is every FPGA able to simulate transmission lines like HDMI or displayport i2s on its I/O ports if there are no dedicated function blocks for this purpose?

What is the case of transferring one batch, e.g. written under XC6SLX9 to, for example, Cyclone I/II/III or others?

What should you really be guided by when choosing a given FPGA, apart from the number of LUT elements?

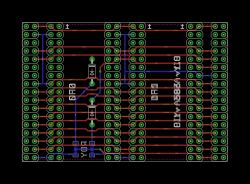

From what I checked, systems that have more than 25k logical units are usually already in BGA housings, hence my question, could it not be possible to separate functional blocks into smaller FPGAs? e.g. tango nano 9k only for graphics, and other smaller ones for the CPU and other peripherals?

What bus should these systems be connected to make everything work properly?