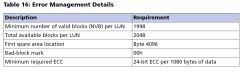

Count yourself what nonsense AI writes. 2048*64*2048 = 2Gb and earlier it writes 4Gb.

Tested experimentally and it is supposed to be LUN=2, 2048, 64, 2048+128.

Tested experimentally and it is supposed to be LUN=2, 2048, 64, 2048+128.

Czy wolisz polską wersję strony elektroda?

Nie, dziękuję Przekieruj mnie tamszmichal wrote:.Count yourself what nonsense AI writes. 2048*64*2048 = 2Gb and earlier he writes 4Gb.

TL;DR: NANDLite v1 erases 512-MBit chips at 4.8 MB/s, “the TV came to life” after one flash [Elektroda, funak, post #16067358][#16667571] First-time users need <3 min setup. Why it matters: hobbyists get pro-level NAND support without €900 lab gear.

• Firmware: NANDLite! _R1.0v1.0b1024a [Elektroda, funak, post #18353353] • Max measured write speed: 2.7 MB/s NAND→XMEGA, 980 kB/s PC link [Elektroda, funak, post #15973950] • Auto-erase rate: 4.8 MB/s on 69 MB ST NAND512W3A [Elektroda, funak, post #16067358] • Supported IC signatures: 70 + (SLC, MLC, ONFI) [Elektroda, funak, post #16449394] • Kit price: approx. PLN 450; worldwide shipping PLN 21 [Elektroda, mailo, post #17314701][#17949208]